🎯 캐시 메모리(Cache Memory)

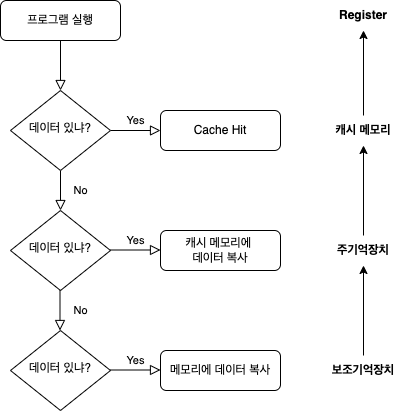

어떤 프로그램을 동작시키기 위해서는 메모리에 적재가 되고 CPU를 할당받아야 동작이 된다. 이때 CPU와 메모리(RAM) 사이에서 활발하게 데이터를 주고받게 되는데 CPU에 비해 비교적 속도가 느린 메모리에 의해서 제대로 성능을 내지 못한다.

캐시 메모리는 CPU와 RAM 사이에서 발생하는 병목 현상을 완화 하고자 사용된다.

캐시 메모리는 CPU 사이에 존재하며 캐시 메모리에 데이터가 존재한다면 메모리에 접근할 필요가 없으므로 성능상 이점을 얻을 수 있다.

캐시 메모리의 목표

✅ 캐시 적중률의 최대화 & 부적중률(不的中律)의 최소화

✅ 캐시 레이턴시의 최소화

✅ 캐시 대역폭의 최대화

✅ 캐시 정책 및 알고리즘의 최적화

✅ 캐시 부적중에 따른 패널티의 최소화

✅ 데이터 일관성 보장

✅ 데이터 일관성에 따른 오버헤드 최소화

적중 & 실패

캐시 적중(cache hit): CPU가 데이터를 요청하여 캐시 메모리에 접근했을 때 캐시 메모리가 해당 데이터를 가지고 있다

캐시 부적중(cache miss): 해당 데이터가 없어서 DRAM에서 가져와야 한다

캐시 적중률(cache hit ratio): (캐시 적중 횟수) / (전체 요청 및 접근 횟수) × 100

- 캐시 부적중의 종류

- Compulsory miss(또는 Cold miss): 해당 메모리 주소를 처음 불렀기 때문에 나는 미스

- Conflict miss: 캐시 메모리에 A 데이터와 B 데이터를 저장해야 하는데, A와 B가 같은 캐시 메모리 주소에 할당되어서 나는 캐시 미스

- Capacity miss: 캐시 메모리에 공간이 부족해서 나는 캐시 미스. 위의 conflict miss는 캐시에 공간이 남아도는데도 불구하고 주소 할당 때문에 나는 미스지만, capacity miss는 주소 할당이 잘 되어있더라도 공간이 부족하면 나는 미스

캐시 작동 원리

캐시 메모리는 데이터 지역성(Locality)의 원리를 이용한다. 데이터 지역성은 시간 지역성(Temporal locality), 공간 지역성(Spatial Locality), 순차적 지역성(Sequential Locality)으로 나뉘다.

시간 지역성(Temporal locality): for나 while 같은 반복문에 사용하는 조건 변수처럼 한번 참조된 데이터는 잠시 후에 또 참조될 가능성이 높다는 것

공간 지역성(Spatial Locality): A[0], A[1]과 같은 데이터 배열에 연속으로 접근할 때 참조된 데이터 근처에 있는 데이터가 잠시 후에 사용될 가능성이 높다는 것

순차적 지역성(Sequential Locality): 분기(branch)가 발생하는 비순차적 실행이 아닌 이상 명령어들이 메모리에 저장된 순서대로 실행하는 특성을 이용한 원리

캐시 배치 정책 (Cache Placement Policy)

흔히 캐시 사상(Mapping) 구조라고도 부르는 정책으로, 여러 캐시 엔트리들을 배치하는 방법을 설명하는 정책이기도 하다.

Direct Mapped Cache: 가장 기본적인 캐시 배치 정책으로, 직역해서 '직접 사상(寫像) 방식'이라고도 한다. DRAM의 여러 주소가 캐시 메모리의 한 주소에 대응되는 다대일(n:1) 방식이다.

Fully Associative Cache: 완전 연관 사상 방식이라고도 부르며, 쉽게 설명하면 비어있는 캐시 메모리가 있으면 그냥 마음대로 주소를 저장하는 방식

Set Associative Cache: 집합 연관 사상 방식이라고도 부르며, Direct Mapped Cache의 장점과 Fully Associative Cache의 장점을 섞었다고 할 수 있는 가장 나중에 나온 방식

Reference

'CS' 카테고리의 다른 글

| 마이크로서비스 아키텍처(MSA) (0) | 2023.04.05 |

|---|---|

| [CS] 패리티 비트 & 해밍 코드 (0) | 2023.03.25 |

| [CS] 고정 소수점 & 부동 소수점 (0) | 2023.03.25 |

| [CS] 중앙기억장치(CPU) (0) | 2023.03.24 |

| [CS] 컴퓨터의 구성 (0) | 2023.03.24 |